# **KSD Photon Counting Integrated Circuit for Intelligent Particulate Sensor** Product Specification

## **General Description**

The KSD is a mixed-signal ASIC for an Intelligent Particulate Sensor (IPS). This ultra-low noise, low power circuit will provide mass concentration/count data of various sized ultrafine particulates (PM0.1 - PM10) in the ambient air with high-accuracy.

The KSD adopts a new photon packet counting architecture to process small photoelectric currents generated by reflected light due to submicron particles, ranging between a few femto to a few pico amperes.

Unlike the conventional scheme of chips, the KSD has an electronic common noise cancellation pre-amplifier to increase SNR. The chip is able to effectively identify actual signals originated from particles that are embedded in noise, which can be a hundred times larger.

The KSD also features five internal discriminators to detect amplitudes of signals proportional to photon energies, and outputs 16-bit binary digital signals to an application system. By using the information of amplitude, width and number of pulses, the chip can provide accurate data to show the mass concentration of particles, their sizes in real-time.

The chip operates at a high frequency (wide bandwidth) to distinguish clustered ultrafine particles, reducing the probability of falsely registering them as a much larger particle.

The KSD is one of the three different versions of Piera System's PCICs (Particle Counting IC).

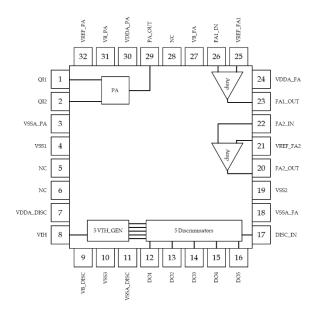

KSD (5mm x 5mm, 32-pin QFN)

## Features

- 11mW low power dissipation

- 3.3V single power supply

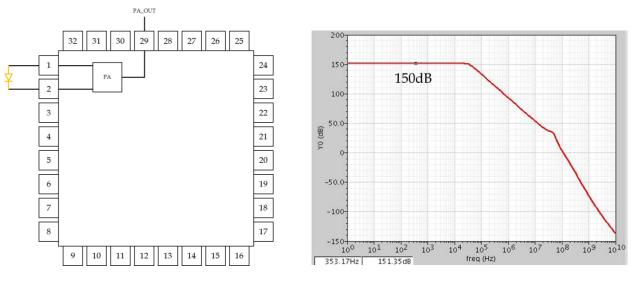

- Gain control (150 240dB)

- High Sensitivity (0.1pA 10pA)

- 5-bin digital outputs & 1 analog output (amplified raw signal from photodiode – can be connected to other discrete amps depending on application

- Binning threshold control (0~3.3V)

- High sampling rate ~1MHz

- Internal noise cancellation

## **Applications**

- Particulate sensor

- Dust sensor

- Noxious gas Spectrum analyzers

# Pin Configuration & Functional Block Diagram

Piera Systems Inc. reserves the right to make corrections, modifications enhancements, improvements and other changes to its products and services at any time and to discontinue any product or service without notice. Please contact Piera Systems anytime to obtain the latest relevant information. We are ready to help you determine which of our solutions will best meet your needs.

# **Recommended Operating Conditions**

| Parameter             | Symbol                      | Min | Тур | Мах | Unit |

|-----------------------|-----------------------------|-----|-----|-----|------|

| Supply Voltage        | VDDA_DISC, VDDA_FA, VDDA_PA | 3.0 | 3.3 | 3.6 | Volt |

| Operating Temperature | T <sub>OP</sub>             | 0   | -   | 85  | °C   |

| Storage Temperature   | Тѕтс                        | -40 | -   | 125 | °C   |

# **Electrical Characteristics**

| Parameter              | Condition                                               | Min | Тур     | Max      | Unit |

|------------------------|---------------------------------------------------------|-----|---------|----------|------|

| Total Current          | VDDA_PA: 2.22mA<br>VDDA_FA: 0.46mA<br>VDDA_DISC: 0.66mA | -   | 3.34    | -        | mA   |

| PA Gain <sup>1)</sup>  | Parasitic Input<br>Capacitance: 100pF                   | 144 | 150-    | 150- 156 |      |

| FA1 Gain <sup>2)</sup> | R2: 5.1kΩ, R2: 510kΩ                                    |     | 40 -    |          | dB   |

| FA2 Gain <sup>2)</sup> | R4: 5.1kΩ, R5: 510kΩ                                    | -   | 40      | -        | dB   |

| VTH <sup>3)</sup>      | -                                                       | 0   |         | 2.5      |      |

| Data Out               | Load capacitance 3pF                                    | 0   | 0 - 3.3 |          | V    |

| Vtrp(+/-)              | -                                                       | 46  | 50      | 55       | mV   |

Note 1): Trans-impedance Amplifier Gain (Vo/Ii)

Note 2): Voltage Gain (Vo/Vi) adjustable by changing the resistors R2 and R5 Note 3): VTH1 ~ VTH5 were evenly spaced, i.e. VTH1 0.5V, VTH2 1.0V, VTH3 1.5V, VTH4 2.0V, and VTH5 2.5V at VTH 2.5V

Piera Systems Inc. reserves the right to make corrections, modifications enhancements, improvements and other changes to its products and services at any time and to discontinue any product or service without notice. Please contact Piera Systems anytime to obtain the latest relevant information. We are ready to help you determine which of our solutions will best meet your needs.

# Pin Description

| Pad<br>No. Pad Nam | Ded Name  | E                                                                       | Value  |         |           |  |

|--------------------|-----------|-------------------------------------------------------------------------|--------|---------|-----------|--|

|                    | Pad Name  | Function                                                                | Min(V) | Typ.(V) | Max(V)    |  |

| 1                  | QI1       | Should be connected to an anode of a photodiode (w/ IO).                |        | -       |           |  |

| 2                  | QI2       | Should be connected to a cathode of a photodiode (w/ IO).               |        | -       |           |  |

| 3                  | VSSA_PA   | Ground pin for preamplifier. Must be connected to 0V.                   |        | 0       |           |  |

| 4                  | VSS1      | Ground pin. Must be connected to 0V.                                    |        | 0       |           |  |

| 5                  | NC        | Should not be connected to anything.                                    |        | -       |           |  |

| 6                  | NC        | Should not be connected to anything.                                    |        | -       |           |  |

| 7                  | VDDA_DISC | Power supply input for discriminator.                                   | 3.0    | 3.3     | 3.6       |  |

| 8                  | VIH       | Threshold voltage setup input voltage. 5 bin threshold voltage control. | 1      | 3       | 3         |  |

| 9                  | VB_DISC   | Bias voltage input for discriminators.                                  | 0.8    | 1       | 1.2       |  |

| 10                 | VSS3      | Ground pin. Must be connected to 0V.                                    |        | 0       |           |  |

| 11                 | VSSA_DISC | Ground pin for discriminators. Must be connected to 0V.                 |        | 0       |           |  |

| 12                 | DO1       | 1 <sup>st</sup> Discriminator output – digital.                         | 0      |         | VDDA_DISC |  |

| 13                 | DO2       | 2 <sup>nd</sup> Discriminator output – digital.                         | 0      |         | VDDA_DISC |  |

| 14                 | DO3       | 3 <sup>rd</sup> Discriminator output – digital.                         | 0      |         | VDDA_DISC |  |

| 15                 | DO4       | 4 <sup>th</sup> Discriminator output – digital.                         | 0      |         | VDDA_DISC |  |

| 16                 | DO5       | 5 <sup>th</sup> Discriminator output – digital.                         | 0      |         | VDDA_DISC |  |

| 17                 | DISC_IN   | Discriminator input.                                                    | 0.2    |         | 3.3       |  |

| 18                 | VSSA_FA   | Ground pin for amplifier. Must be connected to 0V.                      |        | 0       |           |  |

| 19                 | VSS2      | Ground pin. Must be connected to 0V.                                    |        | 0       |           |  |

| 20                 | FA2_OUT   | 2 <sup>nd</sup> Filter & Amplifier output.                              | 0.1    |         | 3.2       |  |

| 21                 | VREF_FA2  | Reference voltage input for 2 <sup>nd</sup> Filter & Amplifier.         | 0.1    | 0.5     | 2.5       |  |

| 22                 | FA2_IN    | 2 <sup>nd</sup> Filter & Amplifier input.                               | 0.1    |         | 3.2       |  |

| 23                 | FA1_OUT   | 1 <sup>st</sup> Filter & Amplifier output.                              | 0.1    |         | 3.2       |  |

| 24                 | VDDA_FA   | Power supply input for Filter & Amplifier.                              | 3.0    | 3.3     | 3.6       |  |

| 25                 | VREF_FA1  | Reference voltage input for 1 <sup>st</sup> Filter & Amplifier.         | 0.1    | 0.5     | 2.5       |  |

| 26                 | FA1_IN    | 1 <sup>st</sup> Filter & Amplifier input.                               | 0.1    |         | 3.2       |  |

| 27                 | VB_FA     | Bias voltage input for Filter & Amplifier                               | 0.8    | 1       | 1.2       |  |

| 28                 | NC        | Should not be connected to anything                                     |        | -       |           |  |

| 29                 | PA_OUT    | Pre-amplifier output (w/ IO)                                            | 1      |         | 3.2       |  |

| 30                 | VDDA_PA   | Power supply input for preamplifier                                     | 3.0    | 3.3     | 3.6       |  |

| 31                 | VB_PA     | Bias voltage input for preamplifier                                     | 0.8    | 1       | 1.2       |  |

| 32                 | VREF_PA   | Reference voltage input for preamplifier                                | 1.24   | 1.26    | 1.28      |  |

Piera Systems Inc. reserves the right to make corrections, modifications enhancements, improvements and other changes to its products and services at any time and to discontinue any product or service without notice. Please contact Piera Systems anytime to obtain the latest relevant information. We are ready to help you determine which of our solutions will best meet your needs.

#### Application Note for Particulate Sensor

Recommended front-end photoelectronic parts

- Laser diode or Infrared diode (IR diode): 800nm 950nm, 5mW 10mW

- Photodiode: matching wavelength to laser diode or Infrared diode (IR diode), < 3mm x 3mm

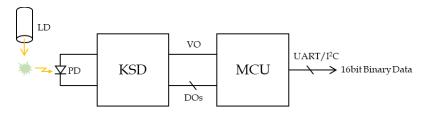

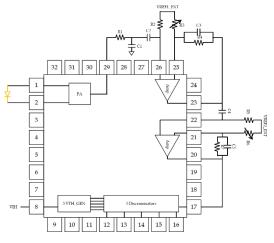

An application block diagram with an MCU is shown in Fig.1. The analog output VO and digital outputs DO1~DO5, can be used to analyze the number and sizes of particles in the air.

Fig. 1. Application circuit with an MCU

#### PA (Preamplifier)

The preamplifier receives photocurrent resulting from reflected light on particles from a photodiode. The current gets amplified by the preamplifier which outputs voltage signal. Customer has freedom to choose a photodiode depending on application. An IR LED or laser diode with wave length of 850nm-940nm is recommended for a typical particle sensor application.

Fig. 2. Preamplifier and a photodiode connection

The gain of the preamplifier (PA) is adjustable by varying the input voltage on VREF\_PA from 1.24V-1.28V.

Piera Systems Inc. reserves the right to make corrections, modifications enhancements, improvements and other changes to its products and services at any time and to discontinue any product or service without notice. Please contact Piera Systems anytime to obtain the latest relevant information. We are ready to help you determine which of our solutions will best meet your needs.

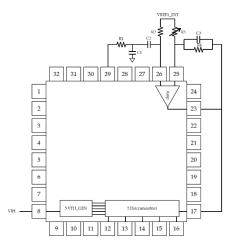

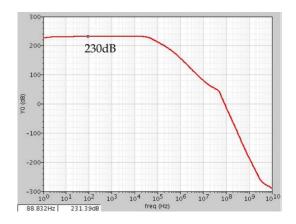

#### FA1 (1<sup>st</sup> Filter and Amplifier)

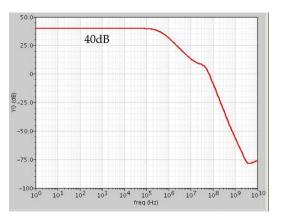

The 1<sup>st</sup> Filter & Amplifying block (FA1) amplifies the output of PA by around 40dB depending on the resistances of R3 (variable) and R4, parallel with the capacitor C3 (0.17nF). The C1 (2.2uF) between the output pin of PA and the input pin of FA1 decouples the DC voltages of PA and FA1. The R1 (10k $\Omega$ ) and C1 forms a low pass filter to increase system stability. The R2 (200k $\Omega$ ) is for supplying reference voltage to FA1.

Fig. 4. Configuration of FA1

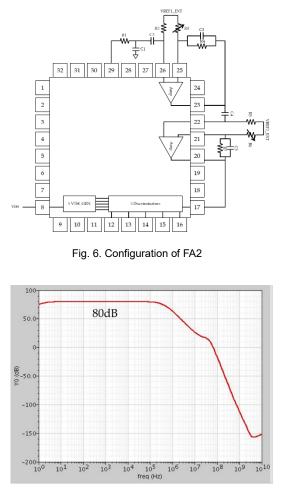

#### FA2 (2<sup>nd</sup> Filter and Amplifier)

A DC decoupling capacitor C4, 0.22uF should be connected in between FA1 and FA2. The FA2 Further provides more gain. With R6 and R7 ( $5.1k\Omega$ and  $510k\Omega$  respectively), connected in parallel with the capacitor C5, 0.34nF, the gain of FA2 is 40dB.

Fig. 7. Gain of FA1 and FA2 combined

Piera Systems Inc. reserves the right to make corrections, modifications enhancements, improvements and other changes to its products and services at any time and to discontinue any product or service without notice. Please contact Piera Systems anytime to obtain the latest relevant information. We are ready to help you determine which of our solutions will best meet your needs.

# VTH

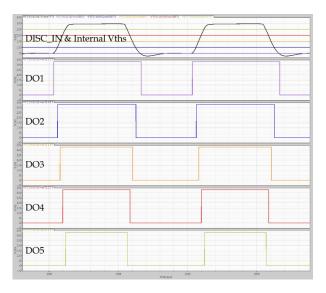

The VTH sets the internal threshold voltage for the 5 discriminators. The 5 VTH\_GEN block generates five different threshold voltages of VTH1-VTH5 that are equally spaced. Digital output pulses are shown in Fig. 8.

Fig. 8. Discriminator output examples

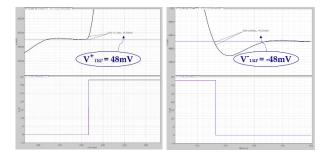

## Hysteresis

KSD has internal hysteresis control to effectively reduce signal transition noise at the threshold point. Fig. 9 shows the trip voltage.

#### **Complete Application Circuit Configuration**

Fig. 10. Complete IC configuration

Fig. 11. Total Gain

Fig. 9. Discriminator output examples

Piera Systems Inc. reserves the right to make corrections, modifications enhancements, improvements and other changes to its products and services at any time and to discontinue any product or service without notice. Please contact Piera Systems anytime to obtain the latest relevant information. We are ready to help you determine which of our solutions will best meet your needs.

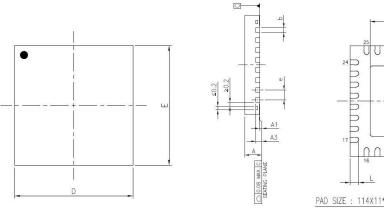

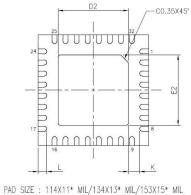

#### **Package Information**

T

|               | PACKAGE TYPE |        |      |            |          |      |          |        |            |  |

|---------------|--------------|--------|------|------------|----------|------|----------|--------|------------|--|

| JEDEC OUTLINE | MO-220       |        |      | MO-220     |          |      |          |        |            |  |

| PKG CODE      | WQFN(X532)   |        |      | VQFN(Y532) |          |      |          |        |            |  |

| SYMBOLS       | MIN.         | NOM.   | MAX. | MIN.       | NOM.     | MAX. |          |        |            |  |

| А             | 0.70         | 0.75   | 0.80 | 0.80       | 0.85     | 0.90 |          |        |            |  |

| A1            | 0.00         | 0.02   | 0.05 | 0.00       | 0.02     | 0.05 |          |        |            |  |

| A3            | 0.           | 203 RE | EF.  | 0.203 REF. |          |      |          |        |            |  |

| b             | 0.18         | 0.25   | 0.30 | 0.18       | 0.25     | 0.30 |          |        |            |  |

| D             | D 5.00 BSC   |        |      | 5.         | 00 BS    | C    |          |        |            |  |

| E             | 5.00 BSC     |        |      | 5.         | 5.00 BSC |      |          |        |            |  |

| е             | 0            | .50 BS | С    | 0.50 BSC   |          |      |          |        |            |  |

| L             | 0.35         | 0.40   | 0.45 | 0.35       | 0.40     | 0.45 |          |        |            |  |

| K             | 0.20         | —      | —    | 0.20       | 1        | -    |          |        |            |  |

| PAD SIZE      | D2           |        |      | E2         |          |      | LEAD     | FINISH | JEDEC CODE |  |

| PAU SIZE      | MIN.         | NOM.   | MAX. | MIN.       | NOM.     | MAX. | Pure Tin | PPF    | JEDEC CODE |  |

| 114X11* MIL   | 2.65         | 2.70   | 2.75 | 2.65       | 2.70     | 2.75 | X        | V      | W(V)HHD-2  |  |

| 134X13* MIL   | 3.15         | 3.20   | 3.25 | 3.15       | 3.20     | 3.25 | V        | V      | W(V)HHD-2  |  |

| 150X15* MIL   | 3.45         | 3.50   | 3.55 | 3.45       | 3.50     | 3.55 | V        | V      | W(V)HHD-5  |  |

| R150X15* MI   | 3.45         | 3.50   | 3.55 | 3.45       | 3.50     | 3.55 | V        | Х      | W(V)HHD-5  |  |

| 153X15* MIL   | 3 20         | 3 25   | 3 30 | 3 20       | 3 25     | 3 30 | V        | V      | W(V)HHD-5  |  |

"\*" is an universal character, which means maybe replaced by specific character, the actual character please refers to the bonding diagram.

Piera Systems Inc. reserves the right to make corrections, modifications enhancements, improvements and other changes to its products and services at any time and to discontinue any product or service without notice. Please contact Piera Systems anytime to obtain the latest relevant information. We are ready to help you determine which of our solutions will best meet your needs.

www.pierasystems.com 代理商联系方式: 样品,评估板,参考设计,报价,技术支持 电话:0755-82565851 邮件:dwin100@dwintech.com 手机:156-2521-4151 网址: www.dwintech.com/Piera\_Systems\_Inc.html 深圳市南频科技有限公司 D-Win Technology(HongKong) Co.,Ltd